Le rayonnement ultraviolet extrĂŞme (en anglais, EUV) correspond Ă un rayonnement Ă©lectromagnĂ©tique de très haute Ă©nergie, avec des longueurs d’onde de 124 Ă 10 nm (avec une Ă©nergie par photon de dix Ă cent fois supĂ©rieure Ă celle de la lumière visible). Cette technologie est en cours de dĂ©ploiement chez bon nombre de fabricants de semi-conducteurs comme Intel ou TSMC. En effet, pour crĂ©er des circuits Ă©lectroniques de plus en plus petits (ou emmagasinant autant de transistors sur une mĂŞme surface) et consommant moins d’Ă©nergie, leur stratĂ©gie principale est d’augmenter la finesse de gravure de leurs circuits : un transistor plus petit a un courant de fuite plus faible, ce qui diminue sa consommation Ă©nergĂ©tique et donc le refroidissement nĂ©cessaire des composants.

Grâce Ă ces nouvelles techniques, ils pourront descendre encore dans leur finesse de gravure, actuellement Ă 14 nm chez Intel (mĂŞme si ces appellations sont trompeuses, chaque fabricant dĂ©cidant de la dĂ©finition physique de cette finesse de gravure). Ă€ titre de comparaison, actuellement, la lithographie moderne se base sur des processus d’ultraviolets profonds, avec une longueur d’onde de 193 nm ; la technologie EUV propose une longueur d’onde Ă 13,5 nm. Initialement, cette dernière Ă©tait prĂ©vue pour le 10 nm en 2016, mais les plans actuels font plutĂ´t Ă©tat d’une arrivĂ©e vers le 7 nm, voire 5 nm (sans compter les pistes d’amĂ©lioration en remplaçant le silicium par un autre semi-conducteur, comme l’arsĂ©niure de gallium et d’indium).

Fin fĂ©vrier a eu lieu la confĂ©rence SPIE pour la lithographie avancĂ©e, oĂą les diffĂ©rents fabricants ont pu prĂ©senter leurs avancĂ©es dans le domaine de la lithographie EUV : c’est l’occasion de se plonger dans les principes de fabrication des processeurs.

![]()

Techniques de lithographie

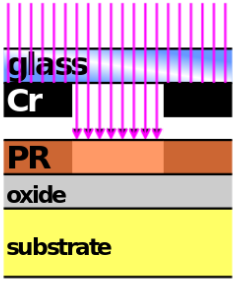

Plus prĂ©cisĂ©ment, la lithographie est la partie de la fabrication de puces qui impose la forme des transistors sur les galettes de silicium, Ă l’aide d’un masque : Ă certains endroits, le masque laisse passer le rayonnement Ă©lectromagnĂ©tique, pas Ă d’autres ; lĂ oĂą il passe, la couche supĂ©rieure de la galette est abĂ®mĂ©e, ce qui forme un morceau de transistor. Le processus est très similaire Ă la photographie argentique, oĂą la lumière expose le film (ce qui correspond Ă la lithographie), des Ă©tapes ultĂ©rieures Ă©tant nĂ©cessaires pour exploiter l’image.

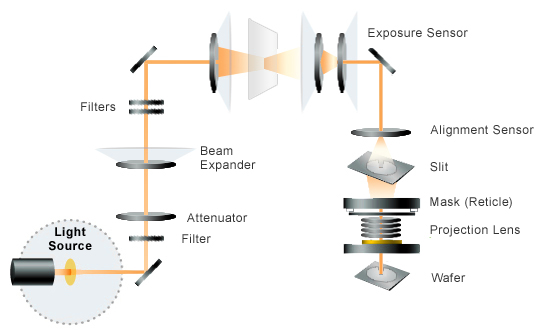

Le problème, c’est que la source d’ondes a une longueur d’onde de 193 nm, alors que les dĂ©tails de gravure sont de l’ordre de 14 nm. Pour compenser la diffĂ©rence, un appareillage d’optique est utilisĂ© pour augmenter la rĂ©solution et limiter la zone d’exposition, tout en rĂ©duisant les aberrations optiques (qui produisent des circuits dĂ©fectueux). Plusieurs passages avec des masques diffĂ©rents peuvent ĂŞtre requis.

Les mĂŞmes techniques sont utilisĂ©es depuis des annĂ©es pour la production de puces, en raffinant l’emploi des diffĂ©rents outils, notamment l’usage de masques de plus en plus nombreux. C’est pourquoi les fabricants ont souvent du mal Ă produire de grandes quantitĂ©s de processeurs rapidement lors du passage Ă la gĂ©nĂ©ration suivante : il faut adapter finement toute une sĂ©rie de paramètres qui limitent le nombre de puces viables produites par ce processus. Une telle transition est donc toujours risquĂ©e d’un point de vue financier.

Et l’EUV ?

Une nouvelle technologie comme l’EUV rĂ©duirait fortement ces risques : grâce Ă la longueur d’onde bien plus courte (13,5 nm), il deviendrait plus facile de gĂ©nĂ©rer des motifs très prĂ©cis sur les galettes sans devoir utiliser un trop grand nombre d’expositions. Cependant, la source lumineuse doit avoir une puissance suffisante : sinon, une exposition prendra trop de temps pour avoir l’effet escomptĂ© sur la galette de silicium. Cette difficultĂ© a beaucoup ralenti l’emploi de l’EUV dans la lithographie actuelle : la production horaire de puces est trop faible pour une Ă©chelle industrielle.

LĂ oĂą les processus actuels utilisent directement un laser dans les ultraviolets (dit « Ă excimère »), une technologie maĂ®trisĂ©e dès les annĂ©es 1970, l’EUV nĂ©cessite un plasma, c’est-Ă -dire de la matière chauffĂ©e Ă très haute tempĂ©rature ou insĂ©rĂ©e dans un champ Ă©lectromagnĂ©tique très intense. ASML produit les machines d’exposition aux EUV utilisĂ©es par tous les fabricants de puces pour le moment.

Il y a deux ans, la puissance maximale Ă©tait de 40 W ; l’annĂ©e dernière, ils arrivaient Ă produire des sources Ă 85 W, maintenant Ă 185 W en laboratoire, puis 250 W d’ici Ă 2017, le niveau requis pour une utilisation commerciale. Des puissances supĂ©rieures sont prĂ©vues dans le laps de temps 2018-2019. Les plans initiaux prĂ©voyaient cependant d’atteindre les 250 W en 2013, puis en 2015… la diffĂ©rence est que la cible est maintenant beaucoup plus proche (il leur reste Ă augmenter la puissance d’un quart, pas de la multiplie par plus de cinq). Ces progrès ont surtout Ă©tĂ© possible en comprenant plus finement la physique derrière la gĂ©nĂ©ration des plasmas.

Globalement, l’arrivĂ©e en production se prĂ©cise. Intel arrive dĂ©jĂ Ă produire des puces 22 nm avec cette technologie. Les machines d’ASML atteignent des taux de disponibilitĂ© de 70 % (ils plafonnaient Ă 55 % il y a deux ans), un seuil encore loin des 95 % des machines actuellement utilisĂ©es en production. Intel et TSMC arrivent Ă produire jusque 500 galettes par jour pendant quatre semaines d’affilĂ©e — chez TSMC, les technologies actuelles permettent de produire 50 000 galettes par jour. TSMC envisage d’utiliser ce processus pour les puces Ă 5 nm, Intel ne se risque pas Ă avancer de date — rejoignant implicitement les rangs des plus pessimistes, qui prĂ©disent que l’EUV n’a de chance d’ĂŞtre utilisĂ© que s’il arrive suffisamment tĂ´t en production, avant d’autres amĂ©liorations.

Sources et images : EUV Lithography Makes Good Progress, Still Not Ready for Prime Time, An Introduction to Semiconductor Physics, Technology, and Industry, EUV Lithography’s Prospects Are Brightening, TSMC and Intel on the Long Road to EUV.

Merci Ă Claude Leloup pour ses corrections.