Malgré quelques superordinateurs utilisant ses processeurs Opteron (notamment, le deuxième le plus puissant), d’autres plus nombreux ses processeurs graphiques Firepro, AMD est loin d’être une figure proéminente du HPC. Dans un article paru dans la revue IEEE Micro (Achieving Exascale Capabilities through Heterogeneous Computing), le fondeur semble vouloir prendre sa revanche, avec une surenchère sur les annonces récentes d’Intel.

Leur prochain APU (accelerated processing unit), mêlant des parties CPU et GPU, sera nommé EHP, pour exascale heterogeneous processor. En peu de mots, de processeur devrait contenir trente-deux cÅ“urs CPU, plusieurs milliers de cÅ“urs GPU avec une mémoire jusqu’à trente-deux gigaoctets, directement intégrée à la puce. Là où Intel prévoit d’utiliser la technologie HMC, AMD profite de son partenariat avec SK Hynix et intègre HBM2. Ce processeur très spécifique pourrait être disponible en 2016-2017 au plus tôt.

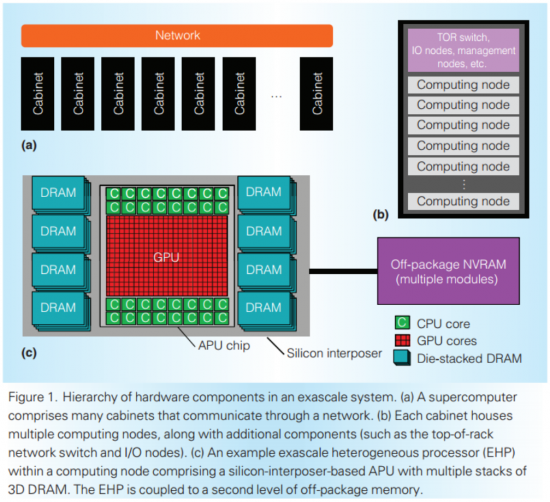

Cette nouvelle puce est exclusivement prévue pour le monde des supercalculateurs, où la course à l’exaflops (un milliard de milliards d’opérations en virgule flottante, avec une précision de soixante-quatre bits) est lancée. La solution conçue par AMD propose des superordinateurs s’étendant sur cent mille nÅ“uds de calcul, chacun fournissant de l’ordre de dix teraflops de puissance de calcul : en comparaison, le superordinateur le plus puissant actuellement, Tianhe-2, s’étend sur seize mille nÅ“uds, chacun fournissant approximativement deux téraflops.

Une telle machine nécessiterait cependant encore beaucoup de recherche, notamment au niveau de l’interconnexion des nÅ“uds, mais également de la consommation énergétique : Tianhe-2 a besoin d’un peu moins de vingt-cinq mégawatts en comptant le refroidissement, un quarantième de la production d’un réacteur nucléaire moyen (utiliser le même système pour atteindre l’exaflops nécessiterait tout un réacteur !). Les projections actuelles font état d’une efficacité de l’ordre de quarante à cinquante gigaflops pare watt pour les nouvelles puces AMD.

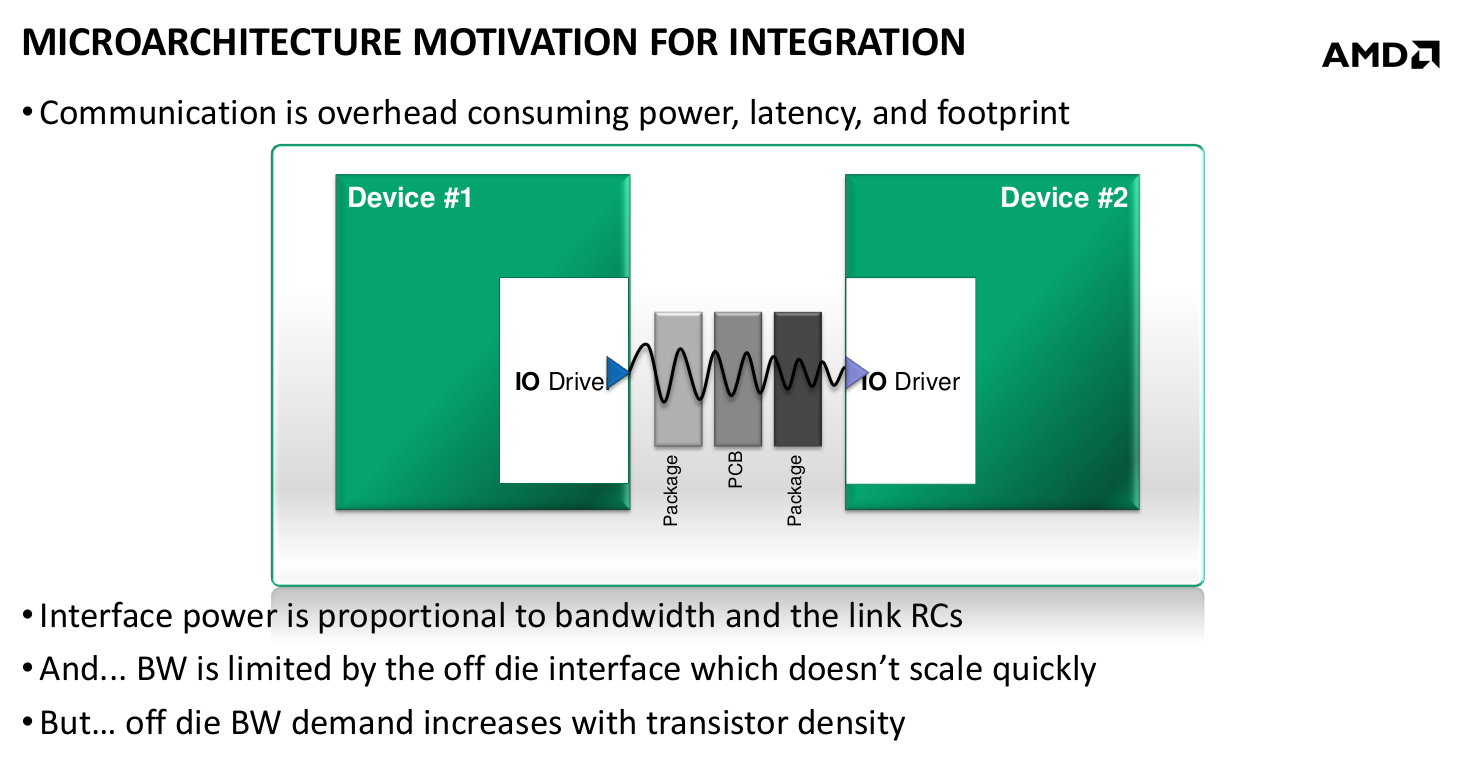

Un nouveau paradigme est donc requis. Il est très similaire à celui déjà utilisé : complémenter les CPU avec des accélérateurs. AMD propose d’intégrer ces accélérateurs directement sur la même puce que le processeur principal, afin notamment de partager la même mémoire et de ne pas être limité par les bus disponibles, y compris à l’intérieur d’un nÅ“ud de calcul — les déplacements de données forment également une bonne partie de la consommation énergétique d’un supercalculateur. D’autres avantages incluent une meilleure densité de performance, mais également l’absence de recours à un système d’exploitation pour une série de tâches (une tâche exécutée sur le GPU pourrait lancer de nouvelles tâches sur le GPU ou le CPU sans nécessiter d’appel aux pilotes ou au système d’exploitation). Les parties CPU pourraient s’occuper des éléments de calcul difficiles à paralléliser, c’est-à -dire les parties qui ne peuvent pas être lancées efficacement sur les accélérateurs.

Cependant, AMD ne propose pas d’intégrer tous les composants dans la puce elle-même : notamment, elle disposerait de huit canaux DDR4 pour l’accès à de la mémoire supplémentaire, ajoutée sous la forme de barrettes plus traditionnelles, jusqu’à atteindre les besoins actuels en mémoire. Chaque canal pourrait adresser jusqu’à deux cent cinquante-six gibioctets de mémoire (c’est-à -dire deux tébioctets en tout). Au niveau de l’architecture globale, chaque cÅ“ur aurait des deux fils d’exécution du cÅ“ur, avec un cache cache L2 d’un demi-kibioctet ; chaque groupe de quatre cÅ“urs partagerait un cache L3 de huit mébioctets. La conception globale pourrait s’accommoder de cÅ“urs x86 ou ARM.

Au vu de ces caractéristiques, il semble peu probable, au vu des techniques de lithographie actuelles, que tout ce petit monde tienne sur la même pastille : le processeur serait séparé en deux parties, chacune ayant seize cÅ“urs, plus la partie GPU, rassemblées par un interposeur, d’ores et déjà nécessaire pour intégrer la mémoire HBM2.

Sources : AMD Reveals the Monsterous ‘Exascale Heterogeneous Processor’ (EHP) with 32 x86 Zen Cores and Greenland HBM2 Graphics on a 2.5D Interposer, AMD’s Exascale Strategy Hinges on Heterogeneity, AMD announces EHP (exascale heterogeneous processor), High performance AMD APU