Pour contrecarrer le mouvement des processeurs graphiques (GPU) dans le domaine du calcul scientifique de haute performance (HPC), Intel a lanc├® en 2013 ses coprocesseurs Xeon Phi. L’id├®e principale est de fournir un grand nombre de c┼ōurs (une soixantaine pour la premi├©re g├®n├®ration), atout principal des GPU (les mod├©les actuels montent ├Ā plusieurs milliers de c┼ōurs). La premi├©re g├®n├®ration de Xeon Phi est notamment utilis├®e dans le supercalculateur chinois Tianhe-2, le plus puissant au monde depuis sa construction en 2013, selon le classement Top500.

Cependant, comme pour les GPU, ces c┼ōurs sont tr├©s diff├®rents de ceux des processeurs plus traditionnels (comme les gammes Core i3-7 d’Intel, par exemple) : ils sont nettement moins v├®loces, avec des fr├®quences de l’ordre du gigahertz ŌĆö le parall├®lisme de ces coprocesseurs est leur principale caract├®ristique. N├®anmoins, contrairement aux GPU, ils peuvent se programmer d’une mani├©re tr├©s similaire aux processeurs classiques.

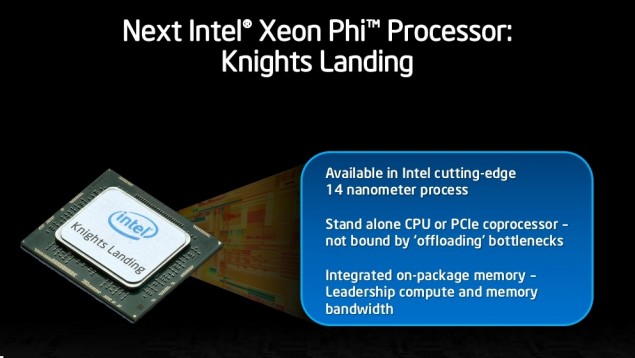

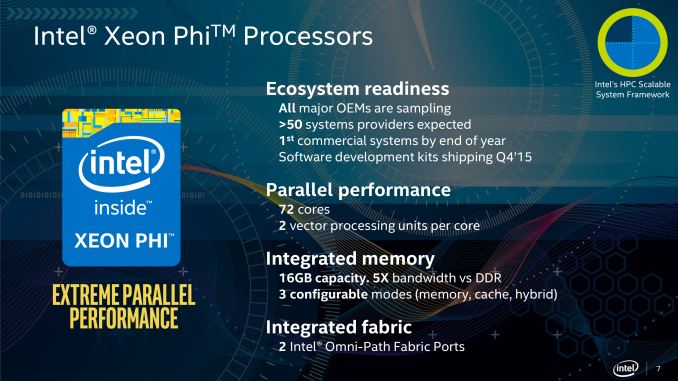

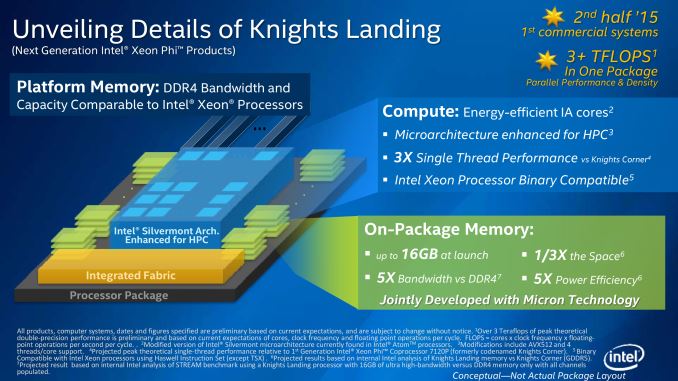

La deuxi├©me g├®n├®ration est sur le point d’arriver, elle devrait ├¬tre commercialis├®e cette ann├®e. Connue sous le nom de code Knights Landing, cette nouvelle mouture tient du superlatif pour ses caract├®ristiques : pas moins de septante-deux c┼ōurs, chacun h├®bergeant deux unit├®s de traitement vectoriel AVX-512 (qui travaillent sur des registres de cinq cent douze bits) ; individuellement, ces c┼ōurs devraient ├¬tre trois fois plus rapides que pr├®c├®demment. La puce elle-m├¬me est grav├®e avec un processus ├Ā quatorze nanom├©tres, ce qui se fait de mieux pour le moment, avec notamment de grands gains en termes de puissance consomm├®e (et de chaleur dissip├®e).

L’architecture pr├®voit aussi des bus DDR4 pour la m├®moire principale, mais surtout seize gigaoctets de m├®moire int├®gr├®e sur la puce elle-m├¬me (avec une bande-passante jusqu’├Ā cinq fois sup├®rieure ├Ā celle de la DDR4, quinze fois par rapport ├Ā la DDR3, encore majoritaire dans les ordinateurs actuels). Cette m├®moire sera ├Ā peu pr├©s aussi rapide que les caches L3 des processeurs actuels (bien qu’ils soient limit├®s ├Ā quelques m├®gaoctets !), avec une bande passante de cinq cents gigaoctets par seconde.

Cette super-m├®moire cache utilisera l’interface HMC (hybrid memory cube), concurrente de HBM (high bandwidth memory) en cours de d├®ploiement sur les processeurs graphiques (les cartes Fury remettent AMD ├Ā l’avant-plan en termes de performance). In fine, un tel processeur pourra proposer une puissance de calcul de l’ordre de trois t├®raflops, c’est-├Ā-dire trois mille milliards d’op├®rations en virgule flottante par seconde.

Une autre nouveaut├® par rapport ├Ā la g├®n├®ration pr├®c├®dente est que ces coprocesseurs pourront servir de processeurs principaux et faire fonctionner le syst├©me d’exploitation de la machine. L’int├®r├¬t majeur est de se d├®barrasser d’une connexion par bus PCI-Express, qui limitait la performance de son pr├®d├®cesseur (une constatation partag├®e par le concurrent NVIDIA, qui s’appr├¬te ├Ā proposer sa technologie NVLink).

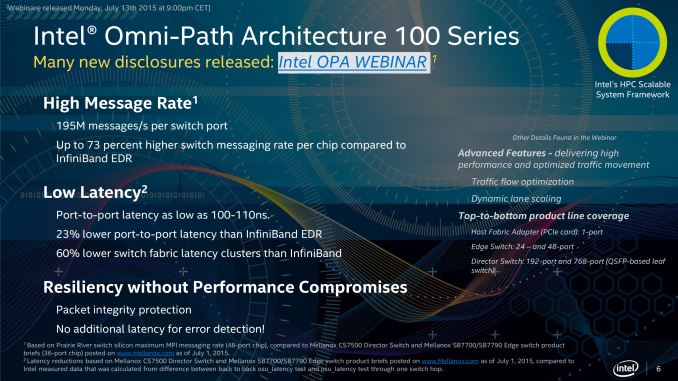

Au niveau de la communication, Intel s’appr├¬te ├®galement ├Ā communiquer plus d’informations sur son Omni Path, une interface d’interconnexion entre n┼ōuds dans un supercalculateur. Intel s’appr├¬te ainsi ├Ā marcher sur les platebandes de g├®ants comme InfiniBand, avec une technologie pr├®sent├®e comme sup├®rieure. Notamment, les latences de communication devraient ├¬tre de l’ordre de cent nanosecondes, quand InfiniBand monte ├Ā presque deux microsecondes, Ethernet ├Ā dix ├Ā cent microsecondes.

Chaque processeur Xeon Phi Knights Landing aura deux ports Omni Path. L’objectif semble ├¬tre l’int├®gration verticale dans les supercalculateurs, Intel ayant annonc├® un partenariat avec HP pour la construction de serveurs autour des technologies HPC d’Intel, rassembl├®es sous le nom de SSF (scalable system framework), dans le contexte de la gamme Apollo de HP.

Sources et cr├®dit images : IntelŌĆÖs Xeon Phi 14nm ŌĆśKnights LandingŌĆÖ Co-Processors Detailed ŌĆō OmniPath Architecture 100 Series and 16GB HMC on a 2.5D Interposer et Quick Note: Intel ŌĆ£Knights LandingŌĆØ Xeon Phi & Omni-Path 100 @ ISC 2015.