En 1964 a ├®t├® construit le premier superordinateur, nomm├® Control Data 6600, avec une puissance de calcul d’un m├®gaflops, c’est-├Ā-dire un million d’op├®rations en virgule flottante chaque seconde (comme additionner deux nombres ├Ā virgule). Il a ├®t├® con├¦u par Seymour Cray, qui a lanc├® la soci├®t├® Cray, connue pour son activit├® dans les supercalculateurs.

Vingt et un ans plus tard, en 1985, la barre du gigaflops a ├®t├® franchie par Cray-2. Actuellement, un processeur haut de gamme (comme un Intel i7 de derni├©re g├®n├®ration) fournit approximativement cent gigaflops.

Une dizaine d’ann├®es plus tard, en 1997, ASCI Red explose le t├®raflops, mille milliards d’op├®rations en virgule flottante par seconde ; dans cette s├®rie de records, c’est le premier ├Ā ne pas ├¬tre associ├® au nom de Cray. Un processeur graphique moderne haut de gamme (comme la GeForce GTX Titan X) d├®passe maintenant quelques t├®raflops.

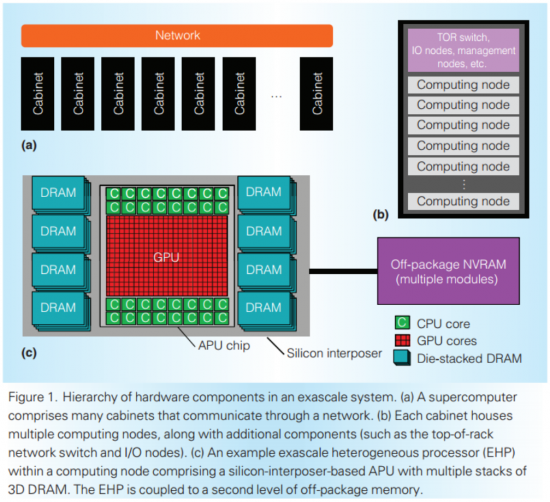

Il y a presque dix ans, Roadrunner atteignant le p├®taflops, en combinant une s├®rie de processeurs similaires ├Ā ceux utilis├®s dans les PlayStation 3. Aujourd’hui, le plus puissant est Tianhe-2, install├® en Chine (alors que les pr├®c├®dents sont am├®ricains), avec une cinquantaine de p├®taflops. La route semble encore longue jusqu’├Ā l’exaflops, c’est-├Ā-dire un milliard de milliards d’op├®rations en virgule flottante par seconde. ├Ć nouveau, les ├ētats-Unis ont lanc├® un projet pour atteindre cette puissance de calcul ├Ā l’horizon 2020 ŌĆö plus particuli├©rement, le D├®partement de l’├ēnergie, le m├¬me ├Ā investir massivement dans un compilateur Fortran moderne libre.

Ces nombres paraissent ├®normissimes : un milliard de milliards d’op├®rations par seconde. Outre les aspects purement informatiques, ce genre de projets a une grande importance pour la recherche scientifique : les laboratoires am├®ricains de l’├ēnergie ├®tudient notamment l’arme nucl├®aire et la destruction en toute s├®curit├® d’ogives ; en Europe, le Human Brain Project vise ├Ā simuler toute l’activit├® c├®r├®brale d’un cerveau humain au niveau neuronal, ce qui n├®cessiterait une puissance de calcul de cet ordre de grandeur.

Comment y arriver ?

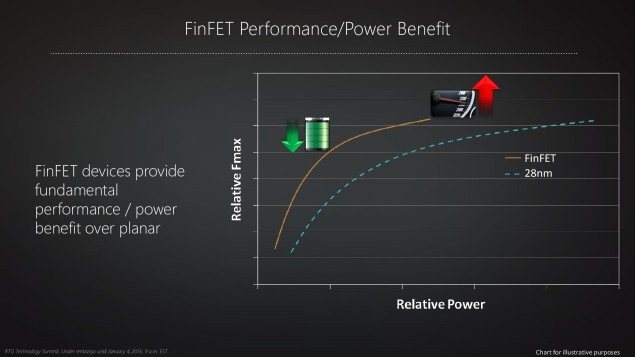

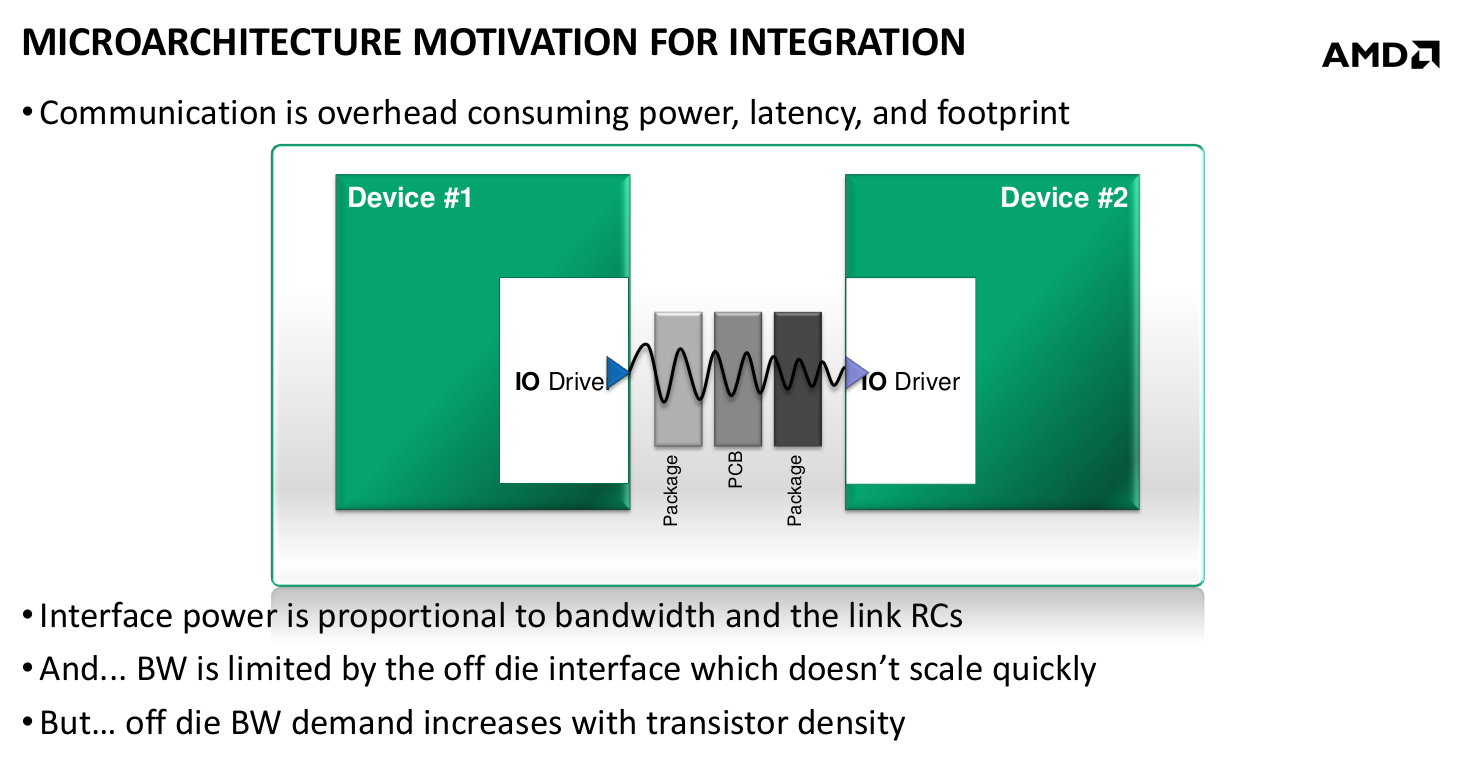

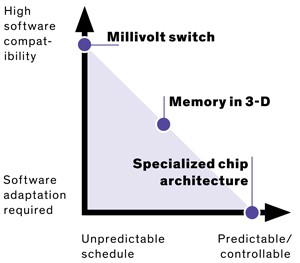

Le D├®partement de l’├ēnergie estime que, actuellement, toutes les technologies n├®cessaires pour construire un tel superordinateur sont r├®unies. Cependant, il serait extr├¬mement difficile de l’alimenter : il faudrait un r├®acteur nucl├®aire complet pour y arriver ! M├¬me si la construction de r├®acteurs fait partie de ses comp├®tences, l’objectif de l’administration est de proposer une machine qui ne consomme « que » vingt m├®gawatts (un r├®acteur nucl├®aire produit g├®n├®ralement mille m├®gawatts). Erik DeBenedictis voit trois technologies pour r├®duire la consommation du facteur cinquante demand├® : des transistors op├®rant ├Ā une tension d’un millivolt, la m├®moire 3D et les processeurs sp├®cialis├®s.

En th├®orie, un transistor peut fonctionner avec des tensions bien plus faibles qu’actuellement, en passant d’un volt ├Ā quelques millivolts ├Ā peine, ce qui augmenterait l’efficacit├® ├®nerg├®tique des processeurs d’un facteur dix ├Ā cent ├Ā court terme (jusqu’├Ā dix mille ├Ā plus long terme !). La diminution de tension a jusqu’├Ā pr├®sent suivi la loi de Moore, suivant la taille des transistors ; cependant, elle est bloqu├®e depuis une d├®cennie au niveau du voltŌĆ” mais personne ne sait comment y arriver. Plusieurs technologies pourraient n├®anmoins passer cette barre :

- les transistors FET ├Ā tunnel ;

- les technologies MEMS, avec des interrupteurs ├®lectrom├®caniques nanom├®triques ;

- la nanophotonique, qui exploiterait de la lumi├©re pour transmettre l’information ;

- la nanomagn├®tique, avec des champs magn├®tiques qui pourraient cr├®er des circuits non volatils.

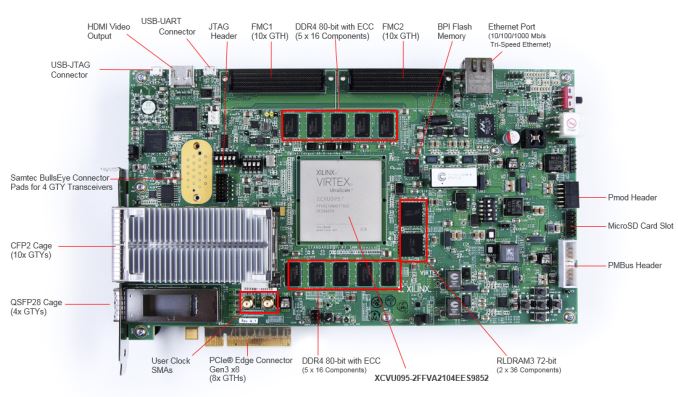

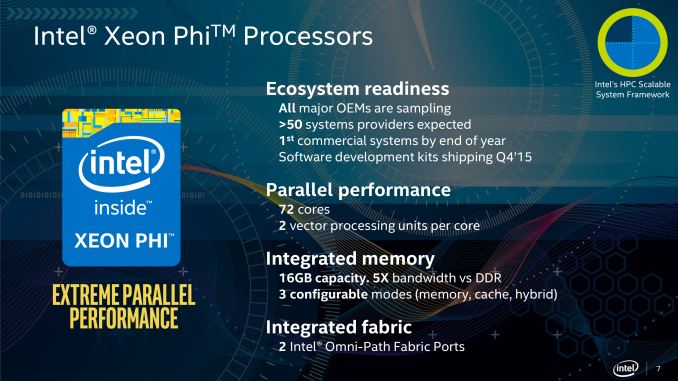

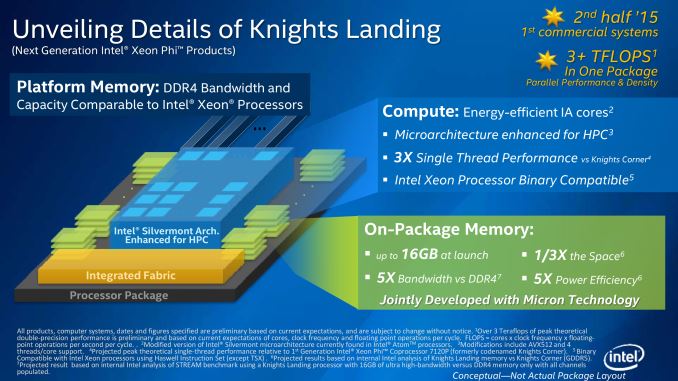

Les m├®moires empil├®es (aussi dites « en trois dimensions ») sont d’ores et d├®j├Ā en cours de d├®ploiement, sous des noms comme HBM ou HMC, dans les processeurs graphiques haut de gamme ou des acc├®l├®rateurs sp├®cifiquement pr├®vus pour le calcul scientifique. Ils permettent une grande r├®duction de la consommation ├®nerg├®tique, d’autant plus enviable que l’objectif de vingt m├®gawatts r├®serve un tiers de la consommation ├Ā la m├®moire. Une autre piste serait d’abandonner autant que possible la m├®moire non volatile, pour passer par exemple ├Ā la m├®moire r├®sistive, comme la technologie Octane d’Intel.

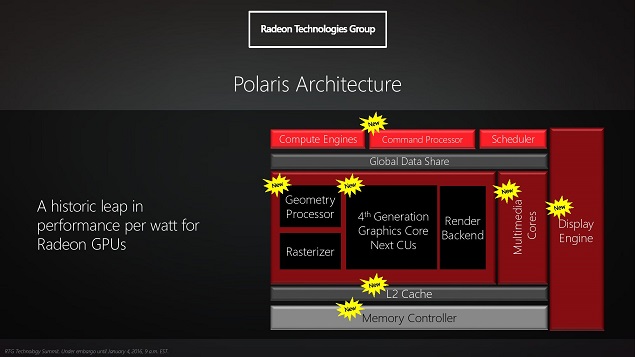

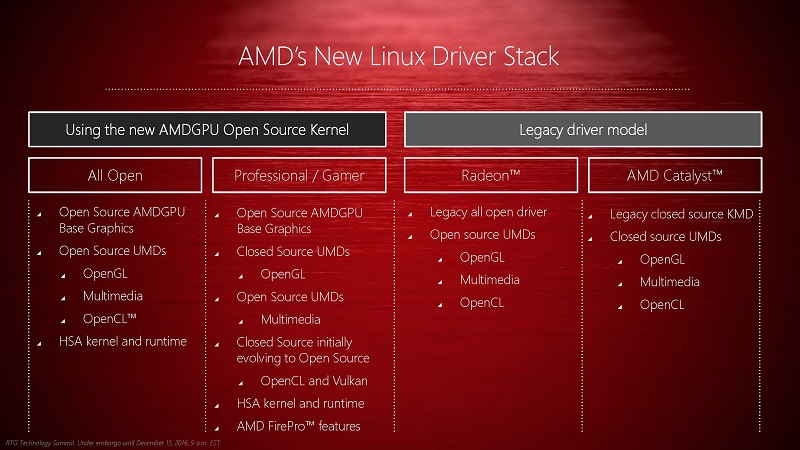

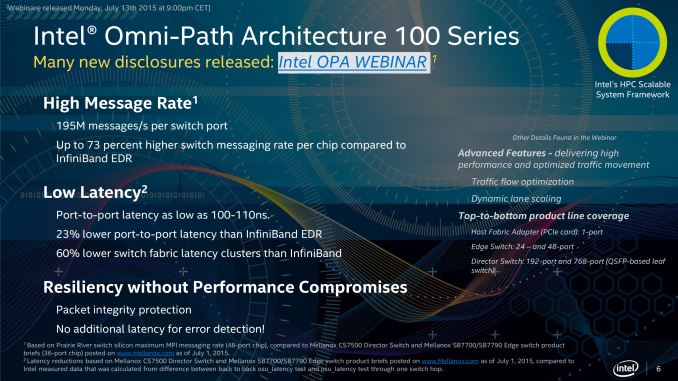

Le troisi├©me axe de recherche propose d’exploiter des architectures beaucoup plus sp├®cifiques aux probl├©mes ├Ā r├®soudre. Elle est d├®j├Ā exploit├®e, puisqu’une bonne partie des superordinateurs les plus puissants utilisent des processeurs graphiques. Cependant, Erik DeBenedictis propose de pousser l’id├®e plus loin encore : installer des processeurs extr├¬mement sp├®cifiques aux t├óches ├Ā r├®aliser, qui seraient activ├®s seulement quand ils sont n├®cessaires. Pour effectuer d’autres types de calculs sur l’ordinateur, il faudrait alors installer d’autres processeurs sp├®cialis├®s, ce qui n’est plus d├®raisonnable actuellement, au vu du prix des puces sp├®cialis├®es.

Des compromis ├Ā r├®aliser

Ces trois pistes ont l’air int├®ressantes, mais n’ont pas du tout les m├¬mes propri├®t├®s quant au mod├©le de programmation actuel : si la physique derri├©re les processeurs change compl├©tement, ils restent programmables de la m├¬me mani├©re ; par contre, pour exploiter efficacement de nouveaux processeurs sp├®cialis├®s, il faudrait changer compl├©tement sa mani├©re de pens├®e. La m├®moire est dans une situation interm├®diaire : empil├®e sur le processeur, les d├®lais d’acc├©s changent radicalement, l’ancien code n’est donc plus aussi efficace s’il tirait parti de ces sp├®cificit├®s, mais continuera ├Ā fonctionner ; au contraire, pour la m├®moire r├®sistive, il n’y aurait plus de distinction entre la m├®moire utilis├®e pour effectuer les calculs et celle pour le stockage ├Ā long terme.

Sources : Three paths to exascale supercomputing (paru en ligne sous le titre Power problems threaten to strangle exascale computing), FLOPS.

Merci ├Ā Claude Leloup pour ses corrections.